|

|

Observation

|

An Engineering_Header contains a minimal core set of observation control parameters. More...

#include <Engineering_Header.hh>

Public Types | |

| enum | Element { LUT_Compressed, Binning_Factor, Delta_Line_Time, TDI_Stages, Trimming, Post_Binned_Lines, FPGA_Code_Version, DLL_Locked, DLL_Reset_Count, DLL_Locked_Once, DLL_Frequency_Correct_Count, ADC_Timing_Settings, Pad, Total_Elements } |

An Element refers to a data containing constituent of a component. More... | |

| enum | DLL_Clock { FIRST_CLOCK, SECOND_CLOCK } |

Selects DLL_Locked{_Once} clock. More... | |

| enum | ADC_Timing_Field { ADC_RESET_TIMING, ADC_IMAGE_TIMING } |

Selects ADC_timing field. More... | |

Public Member Functions | |

| Engineering_Header () | |

| Constructs an empty Engineering_Header. | |

| Engineering_Header (std::istream &stream) | |

| Constructs an Engineering_Header loaded from a data stream. | |

| Engineering_Header (const Engineering_Header &component, bool data_duplicate=true) | |

| Copy constructor. | |

| Engineering_Header & | operator= (const Engineering_Header &component) |

| Assigns another Engineering_Header to this one. | |

| std::string | id () const |

| Provides the class ID on a line followed by the base Data_Component::id. | |

| const char * | name () const |

| Gets the NAME of this class. | |

| u_int_32 | ADC_timing (Index channel, ADC_Timing_Field field) const |

| Gets an ADC timing value. | |

| std::ostream & | print (std::ostream &stream=std::cout, bool verbose=false) const |

| Prints the component structure and contents. | |

| idaeim::PVL::Aggregate * | PVL () const |

| Produces a PVL rendition of the component. | |

| idaeim::PVL::Aggregate * | PVL_description () const |

| Produces a PVL description of the component for a PDS label. | |

| bool | is_valid () const |

| Tests if the component data is valid. | |

Static Public Attributes | |

| static const char *const | ID = "UA::HiRISE::Engineering_Header (1.36 2020/02/14 01:17:18)" |

| Class identification name with source code version and date. | |

| static const char *const | NAME = "Engineering Header" |

| The component name. | |

| static const char * | NAMES [] |

| The name of each Element. | |

| static const Index | COMPONENT_BYTES = ENGINEERING_HEADER_BYTES |

| Total number of bytes in the Data_Block. | |

| static const Index | OFFSETS [] |

| Data_Block data storage address offset for each Element. | |

| static const Index | ARRAY_COUNTS [][2] |

| Data_Block array element value counts each keyed to an Element Index. | |

| static const char *const | FORMAT_FILENAME = ENGINEERING_HEADER_FORMAT_FILE |

| The name of the external PDS format description file. | |

| static const u_int_32 | ADC_TIMING_MASKS [2] = {0x0F, 0xF0} |

| ADC_Timing_Settings field value masks. | |

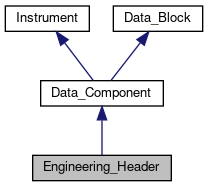

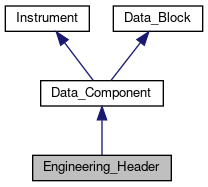

An Engineering_Header contains a minimal core set of observation control parameters.

This Data_Component is the last in the HiRISE observation channel data stream before the image data sequence. Its values are considered to be the most reliable if there is any disagreement with corresponding values from the Science_Channel_Header.

For details consult the "HiRISE Command and Telemetry Handbook" (http://hirise.lpl.arizona.edu/team_site/instrument/Command_and_Telemetry_Handbook/).

Header data block layout:

Offset Size Description ------ ---- ----------- 0 1 LUT Compressed flag 1 1 Binning factor 2 3 Delta line time 5 1 TDI stages 6 2 Trimming value 8 3 Post-binned lines 11 1 FPGA code version 12 1 First 96 MHz DLL lock indicator 0x11 - Locked 0x5A - Out of lock 13 1 Second 96 MHz DLL lock indicator 14 1 DLL reset count 15 1 First 96 MHz DLL locked once indicator 0x11 - Locked once 0x5A - Never locked 16 1 Second 96 MHz DLL locked once indicator 17 1 96 MHz DLL frequency correct count 18 1 Channel 0 ADC timing settings Bits Description ----- ----------- 0 - 3 Reset pulse 4 - 7 Video pulse 19 1 Channel 1 ADC timing settings 20 40 (padding)

N.B.: Data_Block values are MSB ordered.

Note the awkward use of 3 byte integers (odd ;-).

1.28

| enum Element |

An Element refers to a data containing constituent of a component.

Each named Element is an Index into various data sets that define the attributes of a component; including their NAMES, data storage address OFFSETS, and array element value ARRAY_COUNTS. It is the key Index argument of the data access methods.

| enum DLL_Clock |

| enum ADC_Timing_Field |

Constructs an empty Engineering_Header.

The base Data_Component is initialized with the NAMES, COMPONENT_BYTES, OFFSETS, and ARRAY_COUNTS that define an Engineering_Header component structure.

| Engineering_Header | ( | std::istream & | stream ) | [explicit] |

Constructs an Engineering_Header loaded from a data stream.

The base Data_Component is initialized with the NAMES, COMPONENT_BYTES, OFFSETS, and ARRAY_COUNTS that define an Engineering_Header component structure. The stream is then read for COMPONENT_BYTES to fill the data block. Therefore, the stream must be positioned at the beginning of the Engineering_Header data.

| stream | The istream from which to read the component data. |

| Engineering_Header | ( | const Engineering_Header & | component, |

| bool | data_duplicate = true |

||

| ) |

Copy constructor.

| component | The Engineering_Header to be copied. |

| data_duplicate | true if the data content of the copied component is to be duplicated in the copy; false if the data content is to be shared. |

| Engineering_Header & operator= | ( | const Engineering_Header & | component ) |

Assigns another Engineering_Header to this one.

| component | The Engineering_Header to be assigned. |

References Data_Component::operator=().

| string id | ( | ) | const [virtual] |

Provides the class ID on a line followed by the base Data_Component::id.

Reimplemented from Data_Component.

References Engineering_Header::ID.

| const char * name | ( | ) | const [virtual] |

Gets the NAME of this class.

Implements Data_Component.

References Engineering_Header::NAME.

| u_int_32 ADC_timing | ( | Index | channel, |

| ADC_Timing_Field | field | ||

| ) | const |

Gets an ADC timing value.

| channel | The channel number (0 or 1), for which to get the timing value. |

| field | An ADC_Timing_Field selection for either the ADC_RESET_TIMING or ADC_IMAGE_TIMING. |

| ostream & print | ( | std::ostream & | stream = std::cout, |

| bool | verbose = false |

||

| ) | const [virtual] |

Prints the component structure and contents.

Verbose printing includes the class ID and the Pad Element.

| stream | The ostream where the listing will be written. |

| verbose | true if the listing is to be verbose, otherwise some structural details will be omitted for easier human consumption. |

Implements Data_Component.

References ID.

Referenced by list_data(), and list_selections().

| Aggregate * PVL | ( | ) | const [virtual] |

Produces a PVL rendition of the component.

The Pad Element is not included.

Implements Data_Component.

References Engineering_Header::ADC_Timing_Settings, Array::add(), Aggregate::add(), Engineering_Header::Binning_Factor, Vectal< T >::clear(), Engineering_Header::DLL_Frequency_Correct_Count, Engineering_Header::DLL_Locked, Engineering_Header::DLL_Locked_Once, Engineering_Header::DLL_Reset_Count, Engineering_Header::FPGA_Code_Version, Engineering_Header::LUT_Compressed, Engineering_Header::NAME, and Engineering_Header::NAMES.

Referenced by list_selections().

| Aggregate * PVL_description | ( | ) | const |

Produces a PVL description of the component for a PDS label.

The description is an OBJECT that contains the basic PDS parameters required to describe a data product binary data object. The detailed description is referenced as being in an external file named with the value of FORMAT_FILENAME.

References Engineering_Header::FORMAT_FILENAME, Parser::get_parameters(), and Engineering_Header::ID.

| bool is_valid | ( | ) | const [virtual] |

Tests if the component data is valid.

The Binning_Factor, TDI_Stages, and FPGA_Code_Version Elements must have non-zero values. In addition, the Binning_Factor and TDI_Stages Elements must be one of the allowed Instrument constant values.

Implements Data_Component.

References Engineering_Header::Binning_Factor, Instrument::BINNING_FACTORS, Engineering_Header::FPGA_Code_Version, Instrument::TDI_STAGES, Engineering_Header::TDI_Stages, Instrument::TOTAL_BINNING_FACTORS, and Instrument::TOTAL_TDI_STAGES.

const char *const ID = "UA::HiRISE::Engineering_Header (1.36 2020/02/14 01:17:18)" [static] |

Class identification name with source code version and date.

Reimplemented from Data_Component.

Referenced by Engineering_Header::id(), main(), and Engineering_Header::PVL_description().

const char *const NAME = "Engineering Header" [static] |

The component name.

Referenced by Engineering_Header::name(), and Engineering_Header::PVL().

const char * NAMES [static] |

{

"LUT_COMPRESSED",

"BINNING_FACTOR",

"DELTA_LINE_TIME",

"TDI_STAGES",

"TRIMMING",

"POST_BINNED_LINES",

"FPGA_CODE_VERSION",

"DLL_LOCKED",

"DLL_RESET_COUNT",

"DLL_LOCKED_ONCE",

"DLL_FREQUENCY_CORRECT_COUNT",

"ADC_TIMING_SETTINGS",

"PAD",

NULL

}

The name of each Element.

Referenced by Engineering_Header::PVL().

const Index COMPONENT_BYTES = ENGINEERING_HEADER_BYTES [static] |

Total number of bytes in the Data_Block.

Referenced by Observation::components(), Observation::line(), and Observation::PVL_PDS().

{

0,

1,

2,

5,

6,

8,

11,

12,

14,

15,

17,

18,

20,

COMPONENT_BYTES,

0

}

Data_Block data storage address offset for each Element.

const Index ARRAY_COUNTS [static] |

{

{DLL_Locked, 2},

{DLL_Locked_Once, 2},

{ADC_Timing_Settings, 2},

{Pad, 40},

{0,0}

}

Data_Block array element value counts each keyed to an Element Index.

All values of an array element are the same size (the total size of the Element divided by the count of array entries). Any Element not listed here has only one value.

This list must be zero-terminated.

const char *const FORMAT_FILENAME = ENGINEERING_HEADER_FORMAT_FILE [static] |

The name of the external PDS format description file.

Referenced by Engineering_Header::PVL_description().

const u_int_32 ADC_TIMING_MASKS = {0x0F, 0xF0} [static] |

ADC_Timing_Settings field value masks.

1.7.2

1.7.2